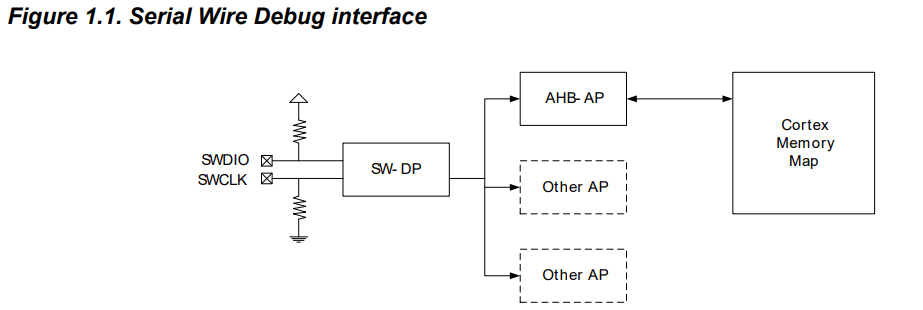

SWD接口和通信实现

空闲态电平

- SWD接口由SWCLK和SWDIO两根信号线组成,

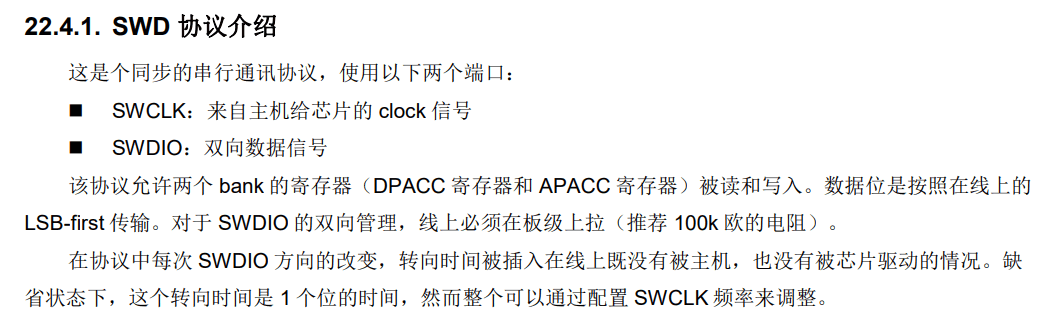

SWCLK调试器给目标芯片的时钟信号,在芯片端需要下拉;SWDIO双向数据信号,在芯片端需要上拉,上/下拉电阻的取值在100K附近即可。 上/下拉电阻取值来自

上/下拉电阻取值来自PY32单片机数据手册:

- 在调试器端,空闲态下:

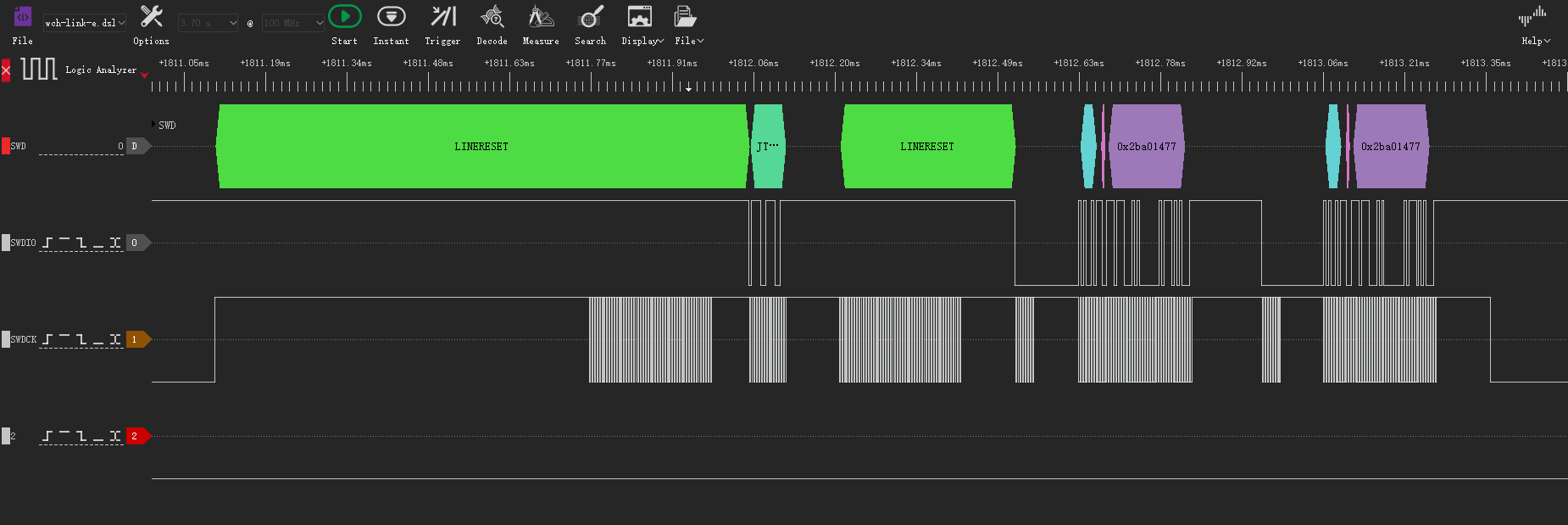

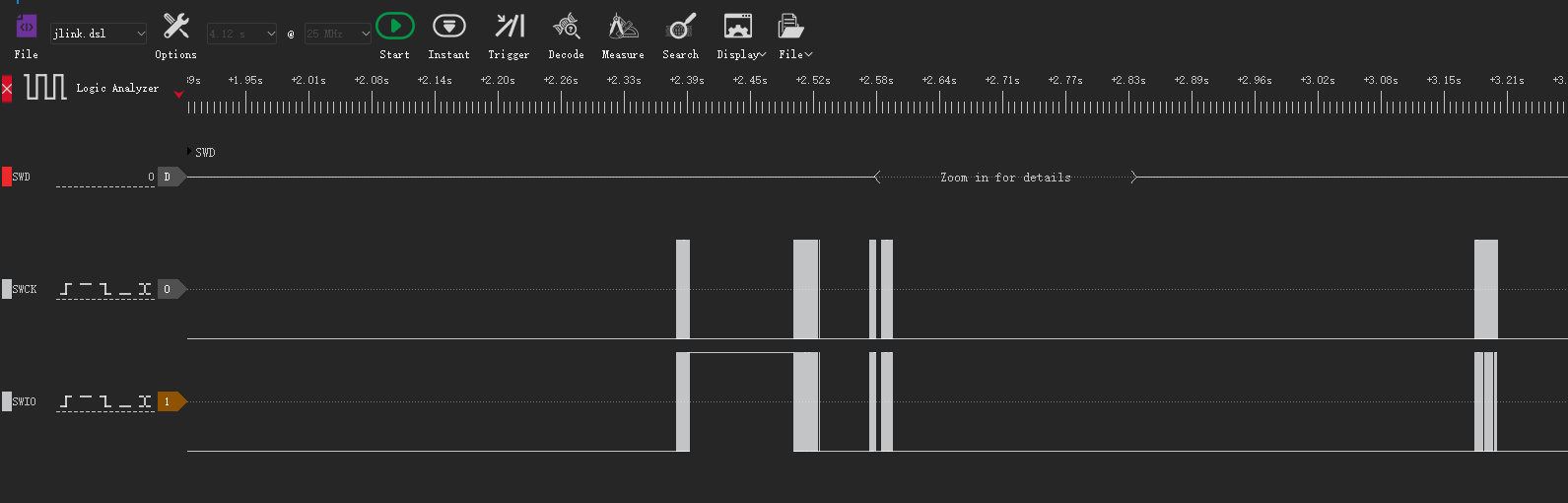

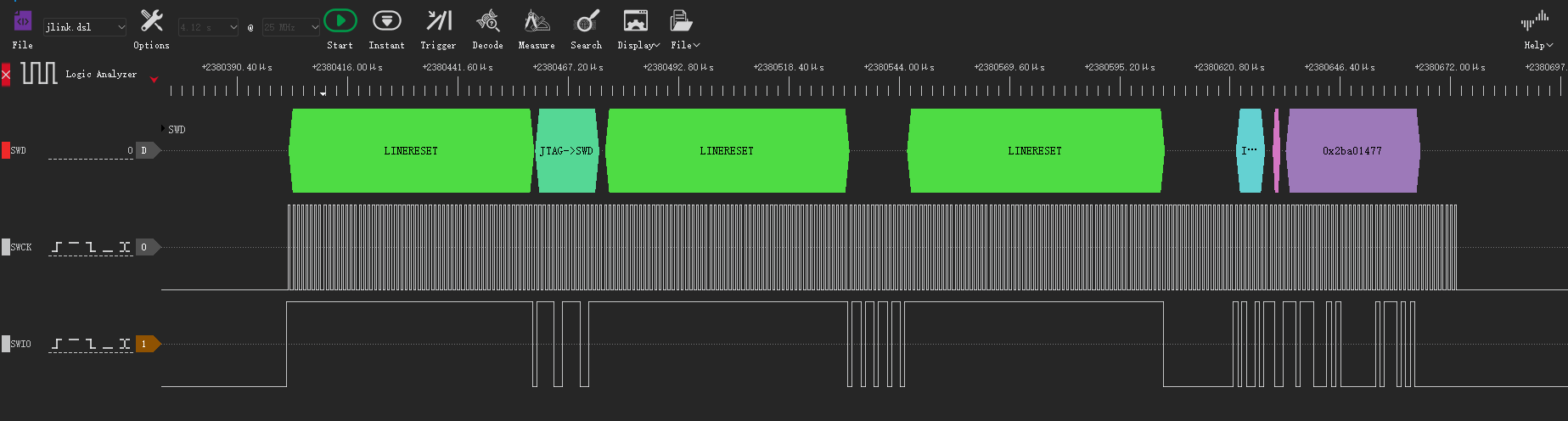

SWDIO可以输出高,SWCLK可以输出高也可以输出低(DAPLINK初始化端口默认输出高,JLINK的SWCLK和SWDIO输出都是低,JLINK和DAPLINK时序不同)。

DAPLINK的配置:

1 | /** Setup SWD I/O pins: SWCLK, SWDIO, and nRESET. |

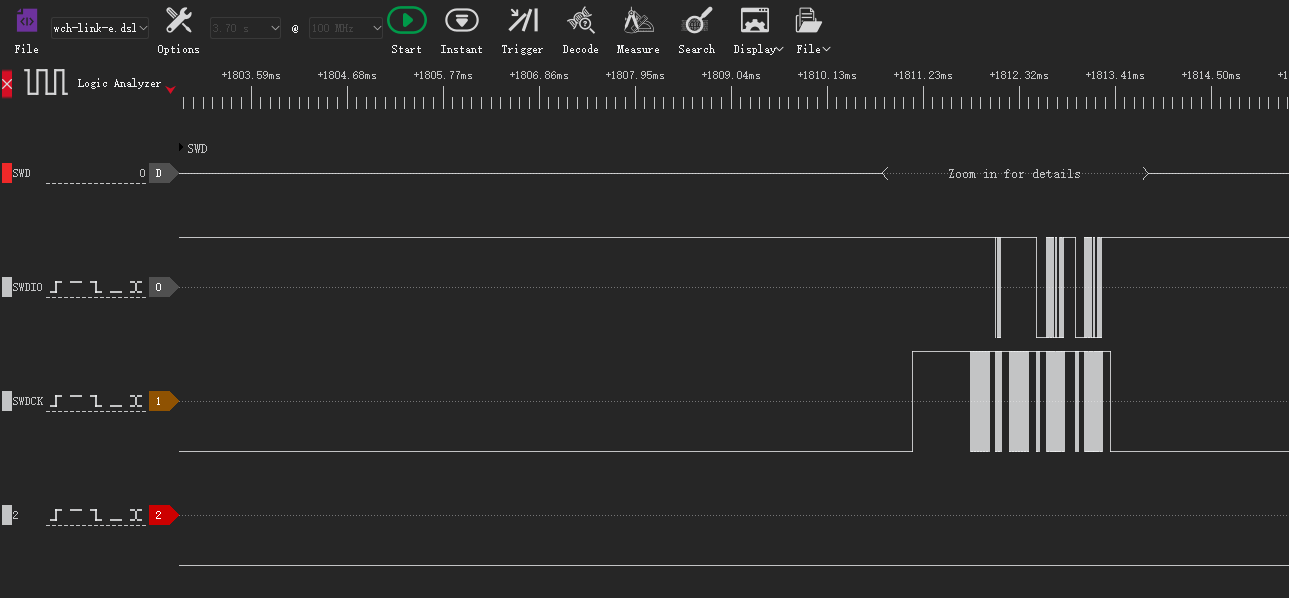

WCH-LinkE工作在DAP模式下的电平实测:空闲态SWDIO为高电,SWCLK为低电平。

JLINK电平实测:空闲态SWDIO和SWCLK都为低电平。

接口模拟

- 纯GPIO模拟,这也是DAPLINK的默认实现方式,只用两个IO,对于SWCLK时钟线,只需要单向输出;但是SWDIO是双向IO,那么调试器就需要对这个GPIO做输入输出切换。该方法优点是简单易实现,缺点是IO翻转频率无法做的很高,输入输出切换时有较大时间消耗。

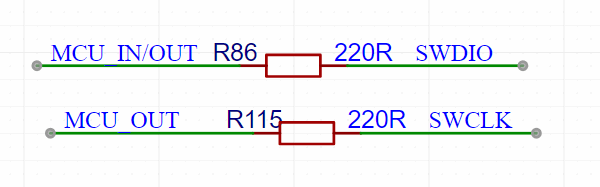

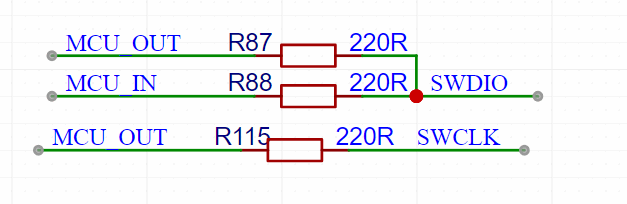

- 纯GPIO模拟,使用三个IO,对于SWCLK时钟线,只需要单向输出;对于SWDIO,使用两个IO,一个输出一个输入,中间串两个或一个电阻防止调试器的输入/输出口灌入大电流。时钟速度仍受GPIO翻转速率限制,优点是省去了IO输入/输出切换的时间。

JLINK接法:

当调试器驱动SWDIO时,信号经过MCU_OUT–>R87–>SWDIO传入目标芯片,同时信号也会经过R88返回到调试器,此时调试器忽略输入。

当目标芯片驱动SWDIO时,信号经过SWDIO–>R88–>MCU_IN被调试器接收,同时信号也会经过R87到达MCU_OUT,由于R87的存在,无论调试器端MCU_OUT之前状态是输出高还是低,都不会造成短路。 DAPLINK接法:

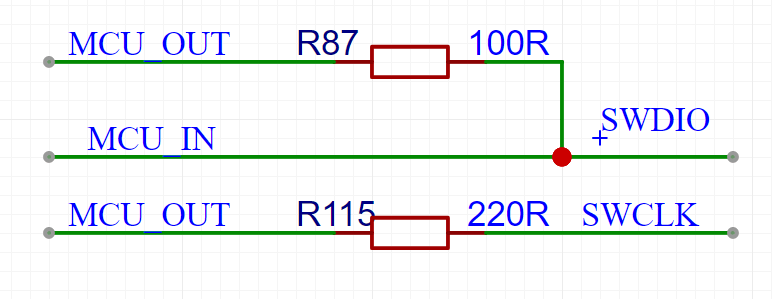

DAPLINK接法:

简化的版本,SWDIO直连调试器输入端,原理和上文类似。 关于电阻的取值:电阻值限制了SWDIO信号线的上升/下降速率,需要高速传输取100R左右的小电阻,代价是动态电流较大,在DAPLINK接法的100R电阻下,调试线长15CM左右,满足10M的IO翻转速率是没有问题的。

关于电阻的取值:电阻值限制了SWDIO信号线的上升/下降速率,需要高速传输取100R左右的小电阻,代价是动态电流较大,在DAPLINK接法的100R电阻下,调试线长15CM左右,满足10M的IO翻转速率是没有问题的。

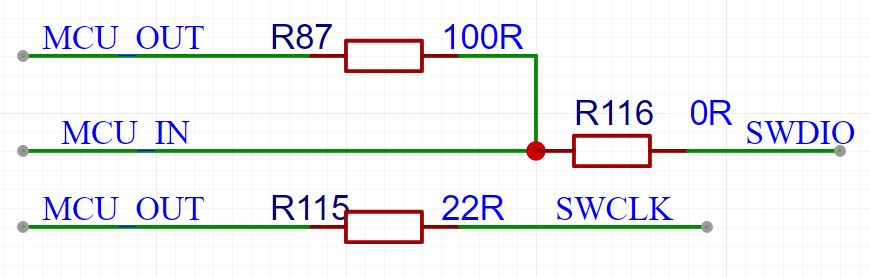

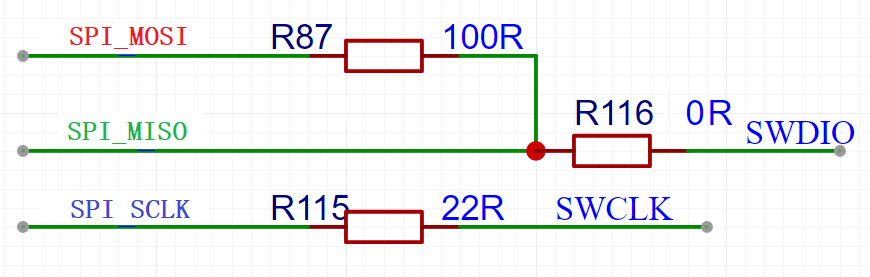

推荐的接法:

满足日常10~20CM的调试线使用,其中0R的电阻预留;当走线较长时,需要实测通信线上升和下降的振铃波形幅度,同时修改R87和R116。

- 利用SPI实现部分硬件加速,适用于常见的只支持

8bit或者16bit固定位宽的SPI外设。这种方案有一定的加速效果,但是使用起来比较麻烦。

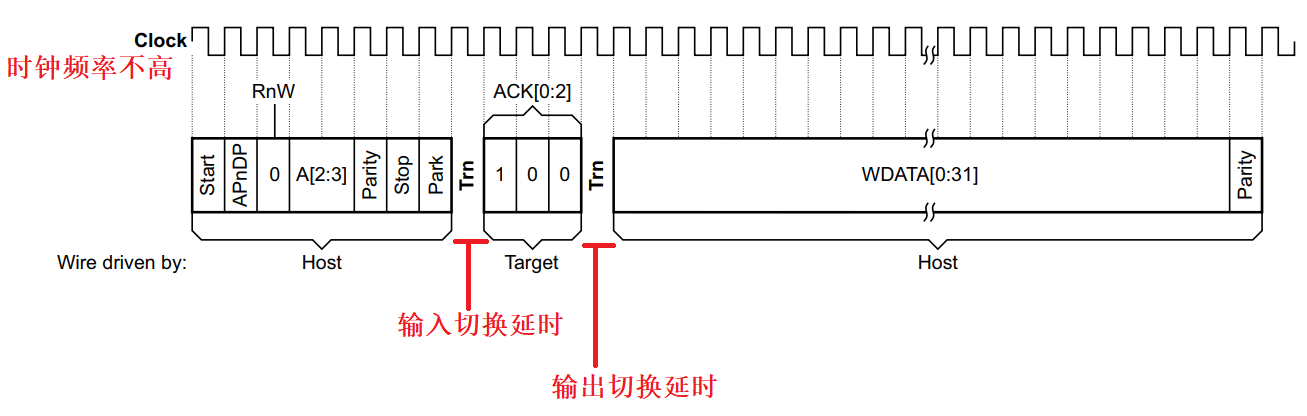

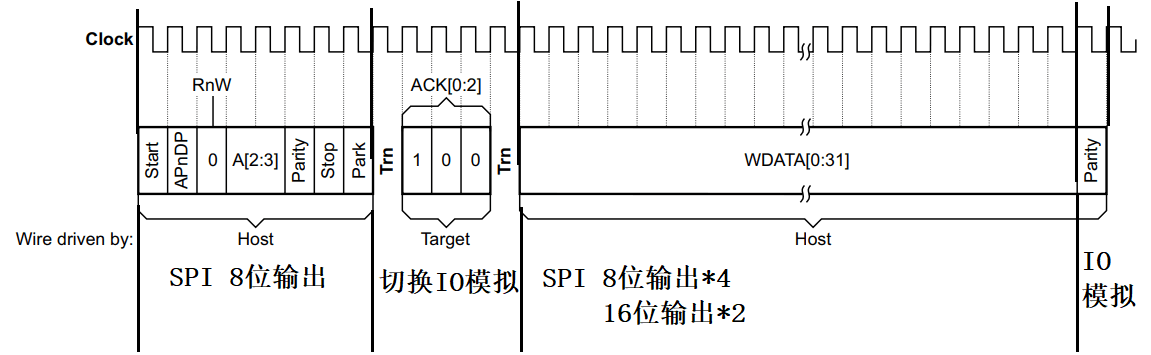

下图是调试器写目标芯片的时序为例:

1:调试器发送的包请求(8bits)由SPI硬件完成

2:转向位(1bit) + 芯片发送的应答响应(3bits)+ 转向位(1bit) 切换到GPIO模拟

3:调试器的数据发送阶段(32bits)由SPI硬件完成

4:校验位(1bit)切换到GPIO模拟

- 完全的SPI硬件加速,硬件连线同上图。例如

STM32F072, STM32F303,STM32F051这种最低支持4bit的SPI外设就可以完全模拟SWD协议各个部分的时序了。

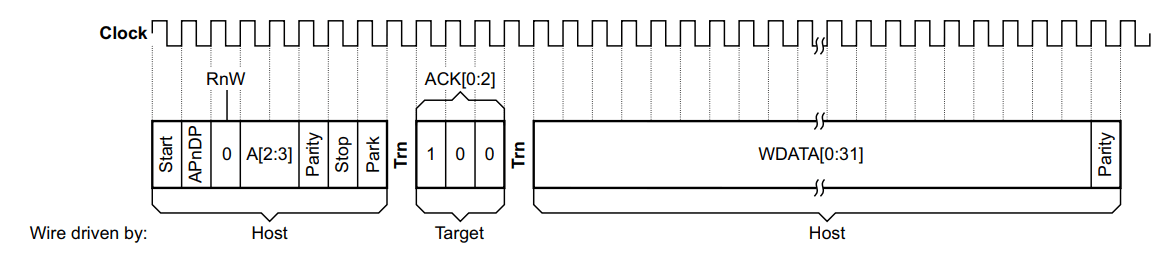

调试器向目标芯片的写操作:8bit写 + 5bit读(丢掉最低位和最高位) + (16bit写 + 8bit写 + 9bit写)。 调试器向目标芯片的读操作:8bit写 + 4bit读(丢掉最低位) + (16bit读 + 8bit读 + 10bit读)。

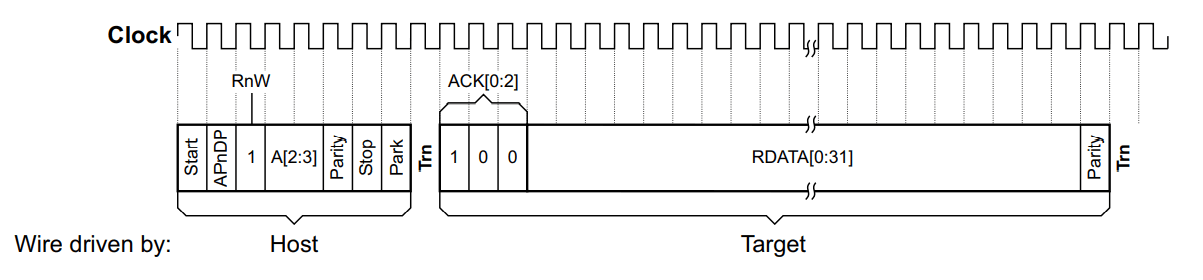

调试器向目标芯片的读操作:8bit写 + 4bit读(丢掉最低位) + (16bit读 + 8bit读 + 10bit读)。

1 | // stm32f0xx_spi.h |

另一款芯片ESP8266的SPI使用FIFO模式操作,支持1bit~512bit任意读写,那么在SWD协议的WDATA段直接发起31bit的传输即可。

信号时序

相关链接(侵删)

欢迎到公众号来唠嗑:

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 赵逸尘个人博客!